解决方案

高效数模混合电路设计与验证

基于Scientific Analog软件平台像数字电路一样设计与验证模拟电路

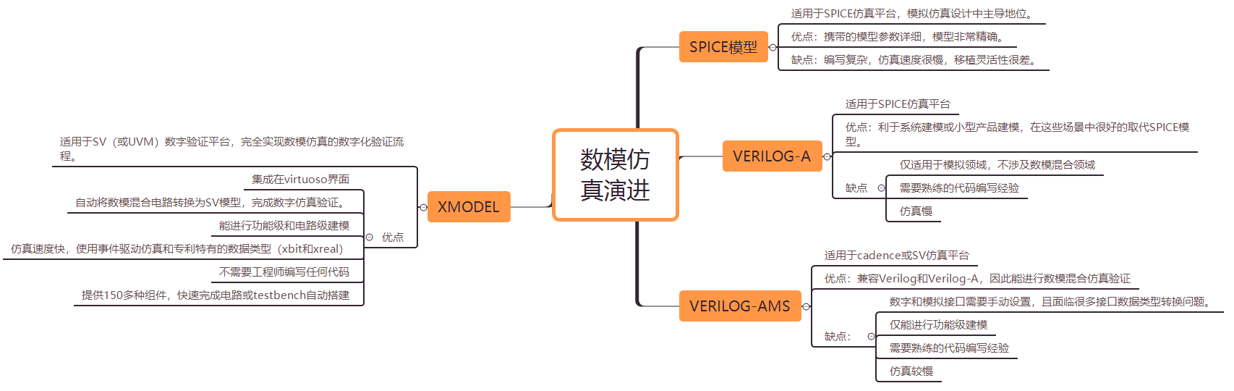

- 模拟仿真及数模混合仿真日益复杂化,推动着仿真工具和代码语言不断更新。下图是模拟和数模仿真验证演进说明。Scientific Analog软件根据各种工具在仿真中的不足进行功能弥补和扩展。

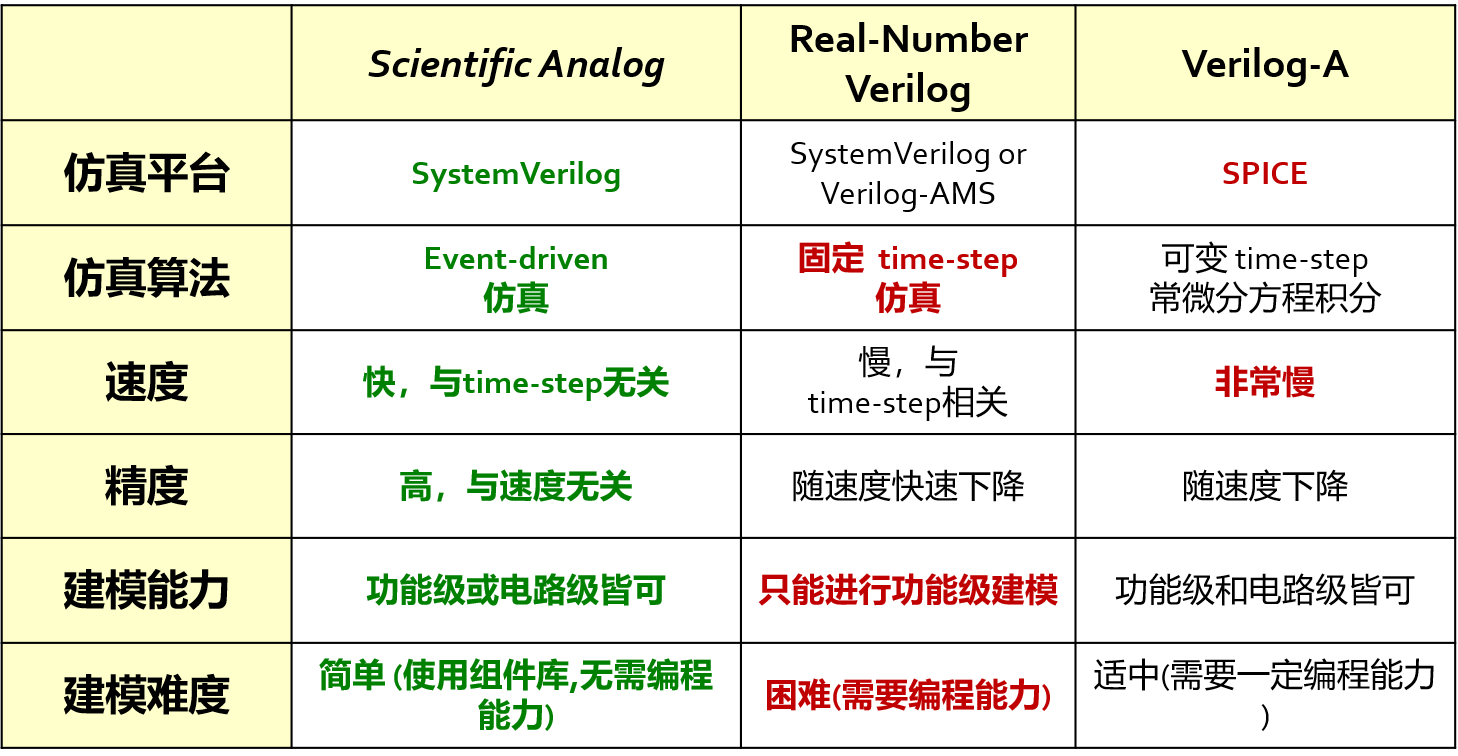

平台对比

Scientific Analog-软件功能模块

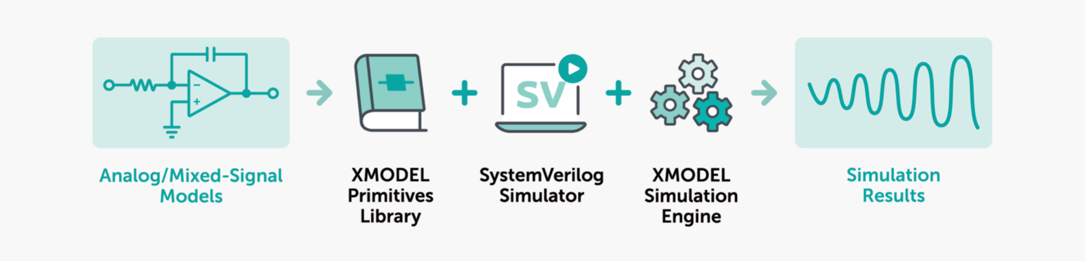

- XMODEL:基于SystemVerilog数字化仿真流程,进行快速、精确的模拟/混合信号仿真验证。

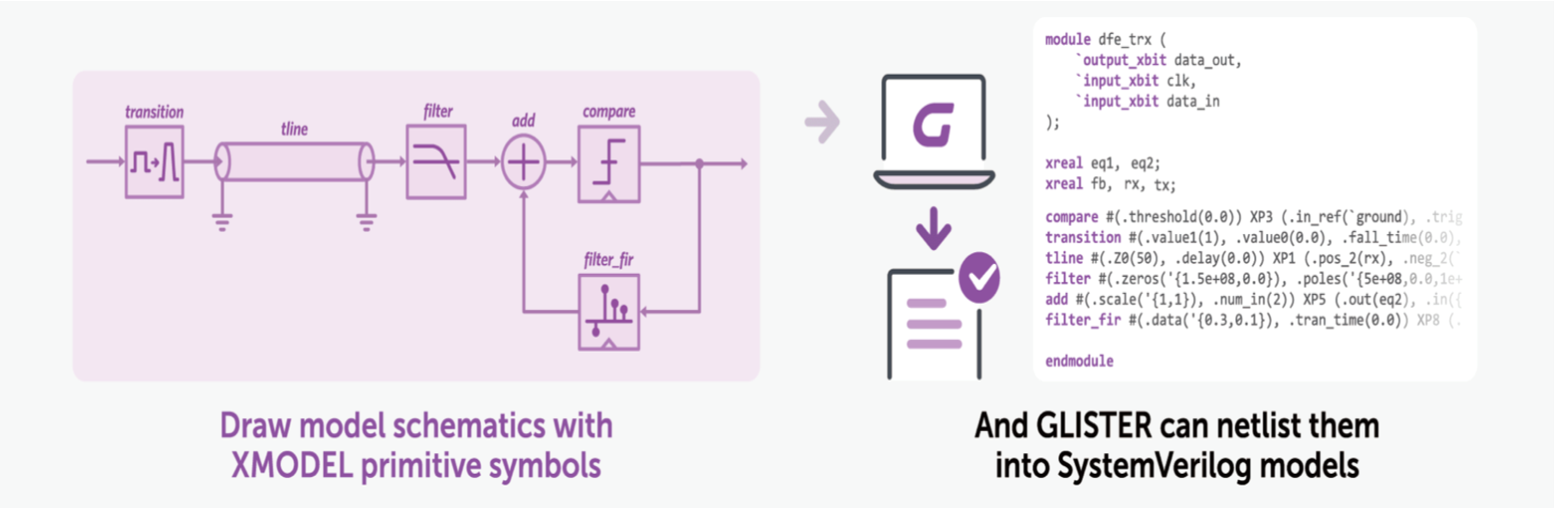

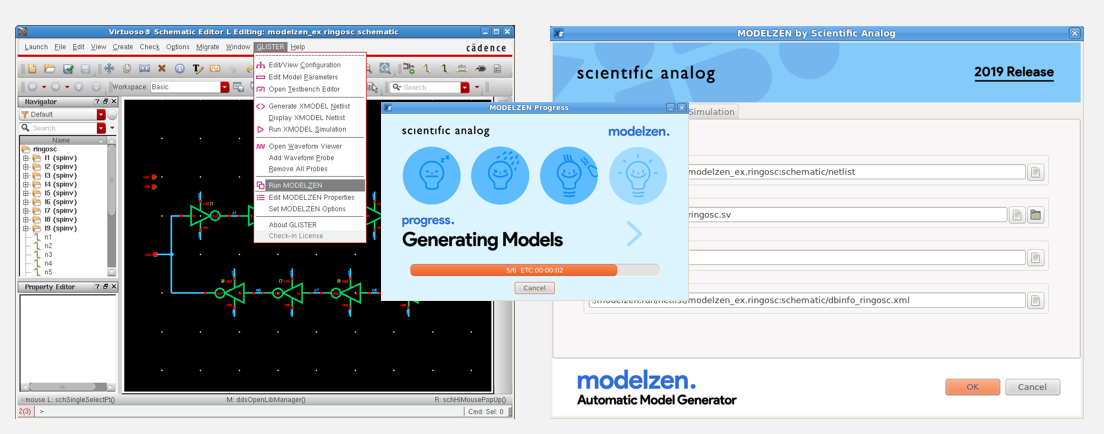

- GLISTER :图形化界面,不需写任何代码,即可从原理图创建top-down的模拟模型。将XMODEL和MODELZEN功能集成在virtuoso中,以图形化界面显示,操作便利。

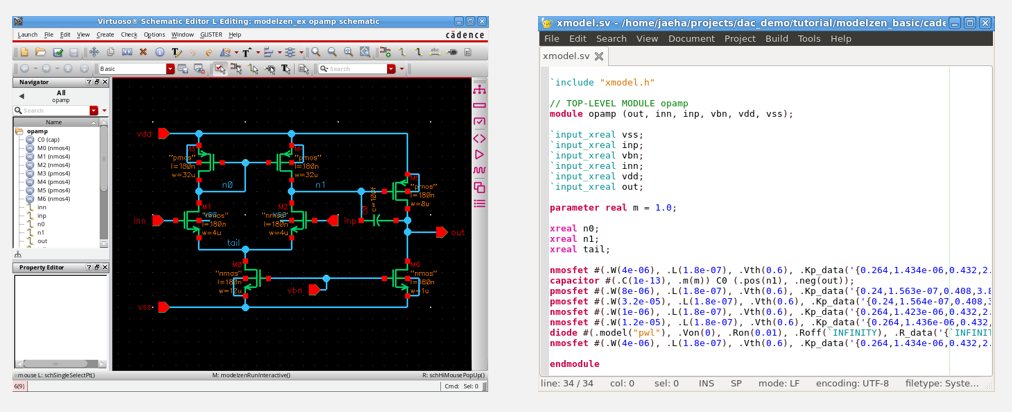

- MODELZEN :从电路原理图或网表自动生成bottom-up的模拟模型

1.XMODEL-事件驱动仿真

- XMODEL仿真引擎将混合电路进行数字化仿真时,采用事情驱动方式提升仿真速度,保证混合电路仿真速度比拟与数字化仿真。

- 首先,软件核心算法中利用xbit和xreal数据类型,并进行了事件定义,如下图所示。它是利用SV提供的数据结构进行变量定义,然后重新定义为新数据类型。仿真时会进行具体实例化。

集成于cadence virtuoso平台,使我们可以用SystemVerilog进行快速而精确的模拟/混合信号仿真

- XMODEL仿真流程如下:将原理图或netlists用内置组件进行映射,转换为数字模型,利用SV仿真器(例如VCS)仿真,采用XMODEL仿真引擎的核心算法(例如事件驱动),SV仿真生成的波形文件在XMODEL自带的波形查看器进行分析。

XMODEL-应用领域

- 架构分析:软件作为top-down tool进行系统功能级验证,来探索可选架构。

- 电路设计:设计人员进行电路设计,软件作为bottom-up tool对模拟电路进行功能级模型提取,然后用于上次系统进行联合验证。

- 系统验证:对于大型数模混合系统,利用软件混合仿真功能进行芯片级验证。其速度比传统验证快10~100倍,且联合仿真完全兼容与数字仿真流程。

2.GLISTER

top-down建模

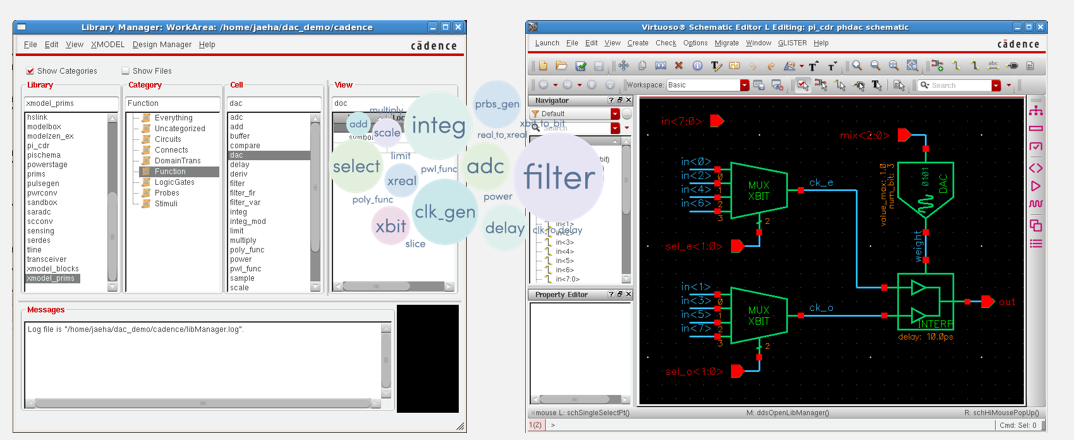

- GLISTER是将XMODEL和MODELZEN功能集成在virtuoso的图形化界面。

- 实现功能如下:

- 利用组件在原理图中搭建电路并生成数字模型,实现top-down建模

- 运行XMODEL仿真,也包括数模混合仿真

- 利用MODELZEN,对电路级设计提取模型

- GLISTER可以在virtuoso原理图中完成top-down建模,不需要编写代码。

- 用户只需简单的将XMODEL提供的组件堆积在原理图中,然后连接在一起即可。

电路建模

- GLISTER可以在virtuoso原理图中完成top-down功能级电路建模,不需要编写代码。

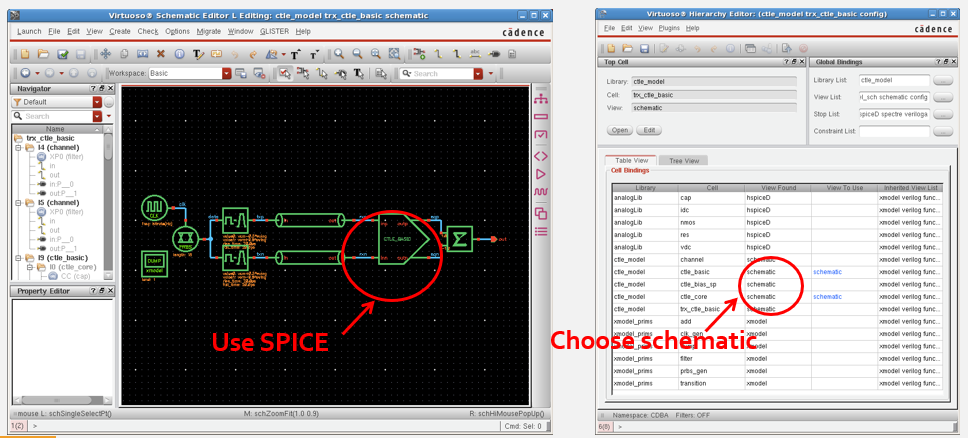

混合电路建模与仿真

- 基于层次配置,GLISTER可以整合xmodel和spice的网表,并进行co-simulation

3.MODELZEN

bottom-up建模

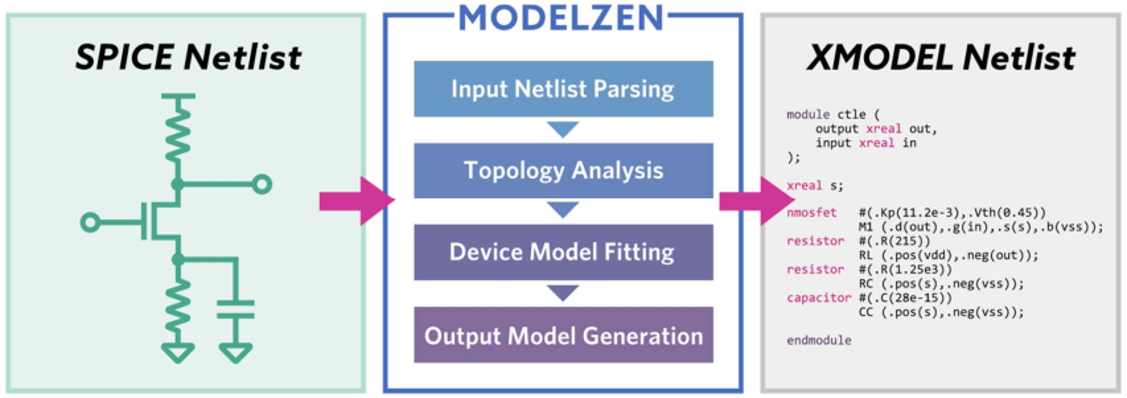

- MODELZEN能从原理图或netlists,自动完成bottom-up建模。

- 既能提取电路级模型,也能提取功能级模型

- 模型参数利用SPICE仿真结合曲线拟合方式进行校准

- 提取的模型仍然利用事件驱动方式进行仿真

GUI建模

- 在原理图的GLISTER界面点击MODELZEN选项,可以对原理图自动生成仿真模型。

bottom-up建模与仿真

- 下图是一个电路级运放电路案例,MODELZEN利用内置电路级组件进行映射,生成数字模型。